Taiwan Semiconductor Manufacturing Company (TSMC) anunció que producirá chips ultraavanzados de 1,6 nanómetros (nm) en 2026. Apuntan a mejorar la densidad y rendimiento de los chips lógicos.

La compañía presentó este miércoles sus últimas tecnologías de proceso de semiconductores, empaquetado avanzado de IC 3D para impulsar la próxima generación de procesadores.

En este Simposio de Tecnología para América del Norte, celebrado en Santa Clara (California) también mostró la tecnología TSMC A16, “que incluye transistores de nanohoja líderes.

TSMC Y UNA INNOVADORA SOLUCIÓN DE RIELES

Estos últimos, según lo detallado, cuentan con una innovadora solución de rieles de alimentación trasero”.

Esta tecnología, que brindará tanto una densidad lógica como un rendimiento “muy mejorados” en chips lógicos, se materializará en la fabricación de procesadores de 1,6 nanómetros (nm).

Asimismo, combinará la arquitectura Super Power Rail de TSMC con sus transistores de nanoplaca y su producción está prevista para 2026.

UNA MEJORA EN LA VELOCIDAD

El fabricante de componentes también apuntó que, en comparación con el proceso N2P, A16 proporcionará una mejora de la velocidad del 8-10% a la tensión positiva de alimentación (VDD)

Asimismo, los próximos chips experimentarán una reducción de la potencia del 15-20 por ciento a la misma velocidad y una mejora de la densidad del chip de hasta 1,10x para centros de datos.

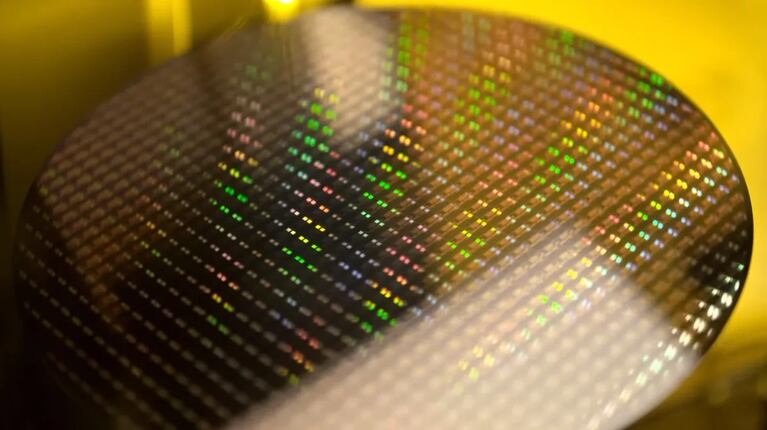

Otra de las novedades presentadas es la tecnología NanoFlex, que impulsará N2 de TSMC y que la compañía ha definido como un “avance en cooptimización de diseño y tecnología”, según el escrito.

TSMC NANOFLEX

TSMC NanoFlex ofrece a los diseñadores de componentes mayor flexibilidad en las celdas estándar N2, así como celdas de mayor altura para maximizar el rendimiento de los componentes.

Esto significa que se puede optimizar la combinación de celdas bajas y altas dentro del mismo bloque de diseño y ajustar sus diseños para tener un equilibrio óptimo de potencia y rendimiento.

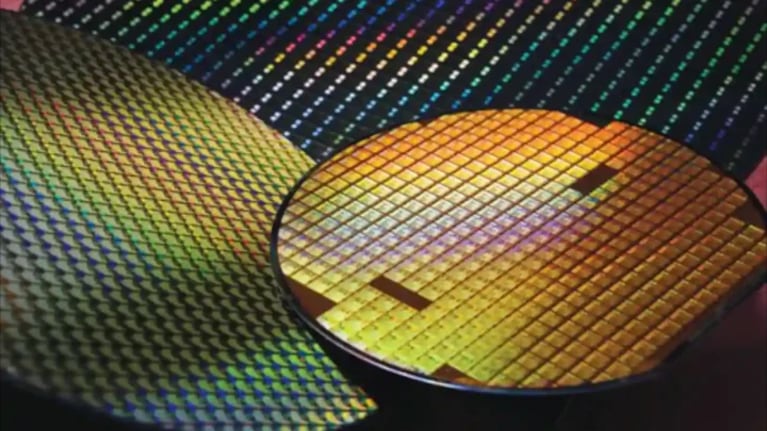

TSMC también sumó N4C a su cartera tecnológica, una extensión de N4P con una reducción del coste de la matriz de hasta el 8,5 por ciento.

COMPATIBLES CON N4P

La han descrito como una ventaja, ya que precisa de menor esfuerzo para su adopción y cuya producción en serie está prevista para 2025.

N4C dispone de IP básicas de área eficiente totalmente compatibles con N4P, con un mejor rendimiento gracias a la reducción del tamaño de la matriz.

Dicha disminución proporciona “una opción rentable para los productos que migren al próximo nodo tecnológico avanzado de TSMC”.

Fuente: EP.